FPGA Bridge

FPGA as a Bridge between 400 MSPS ADC and 10 MHz Throughput DSP

When we talk of precision instrumentation, we are looking at a system that can manage highly complex math-intensive tasks, since the data collected from physical sensors need a complex degree of calculations to be measured. Although a DSP is well suited for extremely complex math-intensive tasks, it cannot process high sampling rate applications due to its serial architecture.

ASIC does meet all the constraints of digital signal processing, however, it lacks flexibility and requires long design cycles. FPGA overcomes the disadvantages of ASIC and DSP with flexibility, time-to-market, risk-mitigation and lower system costs. FPGA is ideal for implementing data formatting, timing, and specialized glue logic needed to connect real-time peripherals like modems, A/D converters and digital receivers to programmable processors.

Now what exactly is an FPGA Bridge and why is it an important design aid? To put this case in point, let me elaborate a design challenge I recently encountered while trying to interface an ADS5474EVM ADC Board and a TMS320C6455 DSK DSP Kit. The DSP required data from an analog sensor for processing. It activated the sensor by providing a capture pulse to it. The sensed analog data was digitized by ADS5474EVM ADC Board at 400 MSPS rate. TMS320C6455 DSK DSP Kit which required this digitized data from ADC for further processing was not able to sample the incoming data at such a high rate. So a need arose to implement a bridge circuit, that could sample data at 400 MSPS and store data equivalent to 20 ms (approx. 8 million samples) from the captured signal. The FPGA Bridge was designed to provide seamless interface between ADS5474EVM ADC Board and TMS320C6455 DSK DSP Kit. The FPGA bridge was a proof of concept that data at 400MSPS from ADC can be sampled at 200 MHz DDR rate by a Spartan 3a DSP (maximum operating frequency is 250 MHz), suitably stored and provided to DSP processor for further processing.

Features Implemented in FPGA Bridge

- Sampling of 14 data bits + 1 Over Range (OVR) bit at 400 MSPS at double data rate (DDR) of Data Ready (DRY) signal.

- 32 bit Asynchronous EMIF interface with TI-DSP.

- To collect data from ADC on request from TI-DSP at 400MSPS (200MHz DDR rate) and transfer it to DDR2 memory

- Designed to store maximum of 40 msec (approximately 16 million samples) of ADC data to DDR2 memory.

- Data stored in the DDR2 memory passed by FPGA to DSP.

- Clock domain crossing handled between ADC interface operating at 200 MHz and rest logic operating at 125 MHz.

Design Flow

- DSP acts as master and maintains the communication between ADC, FPGA and itself.

- FPGA has dedicated 5 write only and 2 read only registers. DSP controls the whole data transfer process by providing appropriate address writes and reads to these control registers thus indicating the start, stop and no of samples to be captured of maximum 40 ms.

- On detection of synchronized hard start capture and soft start capture from DSP, FPGA starts sampling data from ADC.

- FPGA captures 1 zero bit + 14 data bits + 1 Over Range (OVR) bit on both rising and falling edge of the DRY signal through its IOB’s DDR (Double Data Rate) Flip Flops. Thus sampling data at 400 MHz.

- 16 bit data captured on rising and falling edge are combined to 32 bit data and transferred to ADC capture FIFO.

- When the ADC capture FIFO has 4k of data samples that is half of the ADC FIFO, Memory Controller starts transferring data from FIFO to DDR2 memory at DDR rate (64 bits at a time) through MIG interface.

- It stops transferring data to DDR2 when 128 samples are left to be read from Fifo. It then once again waits until FIFO is half full, after which memory controller resumes transferring data from ADC FIFO to DDR2.

- This ping pong mechanism continues until the desired count of data are captured and dumped into the DDR2 memory. As in FIFO, data is dumped at 200 MHz and fetched at 250 MHz so in order to prevent underflow; this ping pong mechanism is implemented.

- Once the data gets captured in DDR2 memory, FPGA interrupts DSP.

- On demand from DSP, FPGA starts transferring 64 bits data to the EMIF FIFO through MIG interface.

- DSP starts capturing data from EMIF FIFO through 32 bit EMIF interface until whole data transfer gets complete.

- FPGA stops transferring data to the EMIF FIFO if the FIFO has 128 write samples left to FIFO full. It then once again starts transferring data to EMIF FIFO when the no of write samples in the FIFO are 128.

- This ping pong mechanism continues until all the data in the DDR2 are fetched by DSP. As the data is fetched at 10 MHz throughput by DSP while data is dumped by Memory controller at 250 MHz, this ping pong mechanism is implemented so that FIFO never overflows.

- Both ADC and EMIF FIFO are implemented such that neither of them will either overflow or underflow.

- FPGA clears the ADC FIFO, EMIF FIFO, and all the internal registers and FSM after every capture.

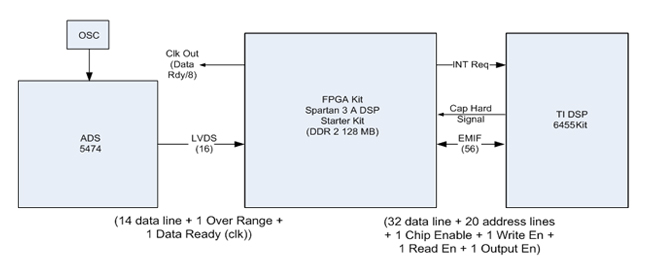

Block Diagram of System Level Interface

The above block diagram shows the top level interface diagram from ADS-5474 kit to FPGA Kit to TI-DSP 6455.

Functional Block Diagram of FPGA Kit and its Interfaces

Internal Architecture

-

- RESET_CLK modules generate synchronous reset and skew free clocks to the respective modules.

- ADC_CAP_IF: LVDS data capture module used to capture ADC sample and transfer 2 samples to Asynchronous FIFO.

- ADC_CAP_FIFO: Asynchronous FIFO with Dual Port BLOCK RAM, the block ram size is 8K x 32 bits at write side and 4K x 64 read side.

- MEMORY_CTRL: Memory Controller Module transfers data from ADC_CAP_FIFO to MIG DDR2 controller and also performs data transfer from MIG DDR2 controller to EMIF_FIFO.

- MIG DDR2 controller transfers data to and from DDR2 memory based on the command-data from Memory Controller.

- EMIF_FIFO: Asynchronous FIFO with Dual Port Block Ram, the block RAM size is 2K x 64 bits at write side and 4k x 32 bits at read side.

- EMIF_IF: 32bits EMIF Interface with Interrupt to TI-DSP and controlling the entire data transfer by generating appropriate control signals to and reception of status signals from ADC capture and Memory controller.

| Module Name | Clock Domain | Input Data Width | Output Data Width |

| ADC CAPTURE Module | In: adc_cap_clkOut: adc_cap_clk | 14Bits data + OVR from ADC IC | 32 Bits (2 Samples of ADC Inputs) |

| ADC_CAP_FIFO | In: adc_cap_clkOut: core_clk | 32 Bits (2 Samples of ADC Input) | 64 Bits to Memory Controller |

| Memory Controller | In: core_clkOut: core_clk | 64 Bits Data from ADC_CAP FIFO | MIG controller (64Bits) |

| Memory Controller | In: core_clkOut: core_clk | 64 Bits Data from MIG controller | 64 Bits data to EMIF FIFO |

| MIG controller (DDR2 Controller Core) | In: core_clkOut: core_clk | 64 Bits data to/from Memory Controller | 32 bits DDR data to DDR2 Memory |

| EMIF FIFO | In: core_clkOut: core_clk | 64 bits data from Memory Controller | 32 bits data to EMIF Controller |

| EMIF Interface | In: core_clkOut: core_clk | 32 Bit Data from EMIF FIFO | 32 Bit Data to TI-DSP using EMIF Protocol. |

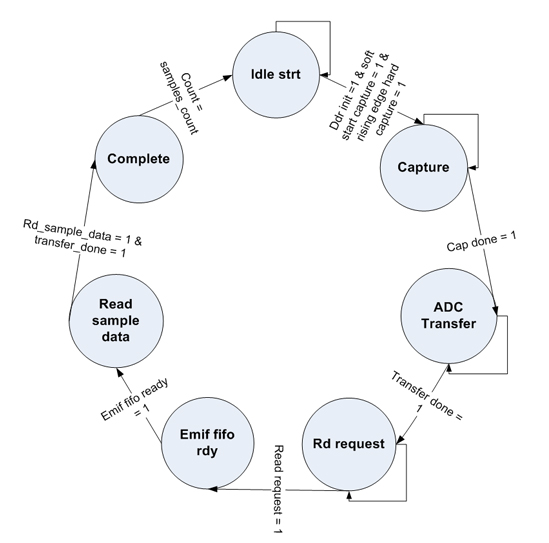

Controlling FSM

Main controlling FSM

Idle State:

Whenever FPGA is reset or powered up just completes a data transfer, FSM is in this state. FSM remains in this state until

- DDR2 is initialized

- Soft Start capture set to 1 in the control register

- Rising edge of the hard capture is detected

When all the above three conditions are satisfied, FSM moves to Capture state and generates capture enable signal for ADC Capture module to start capturing the samples. In this state status register is updated on every clock.

Capture State:

FSM remains in the capture state until it receives capture done signal indicating that the required number of samples have been captured. If capture done was due to forced stop then an interrupt is generated to DSP. Capture enable is made zero and FSM jumps to ADC_transfer state. In this state status register is updated on every clock.

ADC Transfer State:

FSM remains in the ADC Transfer state until it receives transfer done signal indicating that the required number of samples have been transferred to DDR2 memory. An interrupt is generated to DSP if a bit corresponding to transfer done is set in Interrupt mask register. FSM jumps to Read Request state. In this state status register is updated on every clock.

Read Request State:

FSM waits for DSP to write Read Request bit in the control register indicating that DSP is now ready to fetch data. When the Read Request bit is set to 1, FSM jumps to FIFO Ready state and generates the DDR Emif Transfer Enable signal to Memory module to start dumping data from DDR2 memory to EMIF FIFO. In this state, actual samples count register is written.

FIFO Ready State:

FSM waits until EMIF FIFO has 64 samples of data. FSM updates the status register indicating to DSP that data is in the FIFO to be fetched and also generates an interrupt if a bit corresponding to it is 1 in Interrupt mask register. In this state status register is updated on every clock.

Read Sample Data State:

FSM waits for DSP to write Read Sample Data bit in the control register indicating that the DSP has acknowledged FIFO Ready and FSM should continue to dump data from DDR2 memory to EMIF FIFO. FSM remains in this state until it receives DDR EMIF Transfer Done signal indicating that all the samples stored in the DDR2 memory has been transferred to EMIF FIFO. In this state status register is updated on every clock.

Complete State:

FSM waits until all the samples entered in samples count register has been fetched by ADC and then jumps to Idle state. FSM generates an interrupt indicating process complete if a bit corresponding to it is 1 in Interrupt mask register. In this state status register is updated on every clock.

FPGA acting as a bridge was not only able to sample data from ADC at 400 MSPS but was also simultaneously able to transfer and store that data, of maximum 16 million samples to DDR2 memory. Thus in this way DSP was able to process that large chunk of data without loss of any information by fetching it from DDR2 memory through FPGA EMIF interface.

No Comments